Vol.2, Issue.6, Nov-Dec. 2012 pp-4527-4531 ISSN: 2249-6645

## An Optimized BCD Adder Using Reversible Logic Gates

# K.Rajesh<sup>1</sup>, D A Tatajee<sup>2</sup> Department of ECE, A I E T, Visakhapatnam, India,

ABSTRACT: Reversible logic implementation plays an important role in VLSI design. Nowadays, It has voluminous applications in quantum computing, optical computing, quantum dot cellular automata and digital signal processing, low power CMOS design, nanotechnology. Adders are key components in many computational units, so design efficient binary coded decimal (BCD) adder using reversible gates is needed. It is not possible to calculate quantum cost without implementation of reversible logic. This paper proposes a new design for BCD adder that optimized in terms of quantum cost, memory usage and number of reversible gates. The important reversible gates used for reversible logic synthesis are NOT gate, CNOT gate, Toffoli gate, peres gate, TR gate and MTSG gate.

**Key words:** Reversible logic, quantum cost, Toffoli gate, Peres gate, MTSG gate, nanotechnology.

#### I. Introduction

Power dissipation is one of the most important factors in VLSI circuit design. Irreversible logic circuits dissipate KT\*Log2 joules heat energy [1]. Where K is Boltzmann's constant and T is the absolute temperature at which the computation is performed. The amount of energy dissipate in a system bears a direct relationship to the number of bits erased during the computation. Some bits erased means some information is lost. Bennet showed that the KT\*Log2 joules energy dissipation would not occur if a computation is carried out in a reversible manor. Reversible computation can be performed through circuits that do not lose information [2].

As the Moore's law continues to hold, the processing power doubles every 18 months [1]. The current irreversible technologies will dissipate a lot of heat and can reduce the life of the circuit. The reversible logic operations do not erase the information and dissipate very less heat. Thus, Reversible logic is likely to be in demand in high speed power aware circuits. The main challenges of designing reversible circuits are to reduce number of gates, memory usage, delay and quantum cost. This paper presents a new design of reversible BCD adder. The hardware complexity of this design is very less when compared to the existing once.

#### II. Basic Definitions of Reversible Logic

In this section, the basic definitions and ideas to the reversible logic and few reversible gates which are used and relevant with this research work.

#### 2.1. Reversible logic

It is an n-input, n-output logic function in which there is a one-to-one correspondence between the inputs and outputs [3]. Because of this one to one mapping the input vector can be uniquely determined from the output vector.

#### 2.2. Quantum cost

Quantum cost refers of to the cost of circuit in terms of the cost of primitive gate. It is calculated knowing the number of primitive reversible logic gates required to realize the circuit [4].

#### **2.3. Delay**

The delay of a logic circuit is the maximum number of gates in a path from any input line to any output line. This definition is based on the following assumptions [2]

- (i) Each gate performs computation in one unit time.

- (ii) All inputs to the circuit are available before the Computation begins.

#### 2.4. Hardware complexity

Hardware complexity refers to the total number of logic operations in a circuit. Means the total number of AND, OR and EXOR operation in a circuit.

#### 2.5. Ancilla inputs

This refers to the number of inputs that are to be maintaining constant at either 0 or 1 in order to synthesize the given logical function [5].

#### 2.6. Garbage outputs

Garbage outputs are the unutilized outputs in reversible circuits which maintain reversibility but do not perform any useful operations [6].

Vol.2, Issue.6, Nov-Dec. 2012 pp-4527-4531

## ISSN: 2249-6645 **III. Reversible Logic Gates**

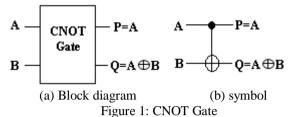

#### 3.1. CNOT GATE

CNOT gate is also known as controlled-not gate. It is a 2\*2 reversible gate. The CNOT gate can be described as:

$$IV = (A, B)$$

(1)

$$Ov = (P = A, Q = A \oplus B)$$

(2)

IV and Ov are input and output vectors respectively. Quantum cost of Cnot gate is 1[14]. Figure 1 shows a 2\*2 CNOT gate and its symbol.

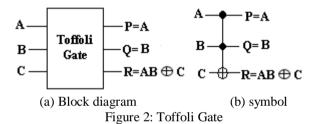

#### 3.2. TOFFOLI GATE

Toffoli gate is a 3\*3 reversible gate [14]. The input vector is I (A, B, C) and output vector is O (P, Q, R). The Toffoli gate can be described as:

Iv =

$$(A, B, C)$$

(3)

Ov=  $(P=A, Q=B, R = AB \oplus C)$  (4)

Quantum cost of Toffoli gate is 5. Figure 2 shows a 3\*3 Toffoli gate and symbol.

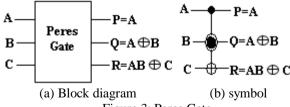

#### 3.3. PERES GATE

Peres gate is a 3\*3 reversible gate. It is also known as New Toffoli gate. It is constricted from CNOT gate and Toffoli gate [2]. The Peres gate can be described as:

$$Iv = (A, B, C)$$

$$Ov = (P = A, Q = A \oplus B, R = AB \oplus C)$$

(5)

(6)

$I_v$  and  $O_v$  are input and output vectors orderly. Quantum cost of Peres gate is 4. The Peres gate and its symbol is shown in Figure 3.

Figure 3: Peres Gate

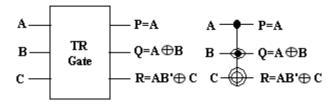

### 3.4. TR GATE

TR gate full name is Thapliyal-Ranganathan gate. It is a 3\*3 reversible gate [8]. The TR gate can be described as:

$$IV = (A, B, C)$$

(7)

$Ov = (P = A, Q = A \oplus B, R = AB' \oplus C)$  (8)

I<sub>V</sub> and O<sub>v</sub> are input and output vectors orderly. Quantum cost of TR gate is 4. The TR gate and its symbol are shown in figure 4.

www.ijmer.com

Vol.2, Issue.6, Nov-Dec. 2012 pp-4527-4531 ISSN: 2249-6645

(a) Block diagram

(b) symbol

Figure 4: TR Gate

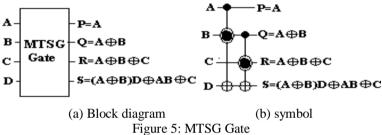

#### 3.5. MTSG GATE

MTSG gate is a 4\*4 reversible gate. The MTSG gate can be described as:

$$Iv = (A, B, C, D)$$

$$(9)$$

Ov =

$$(P = A, Q = A \oplus B, R = A \oplus B \oplus C)$$

(10)

$$S = (A \oplus B)D \oplus AB \oplus C) \tag{11}$$

I<sub>V</sub> and O<sub>v</sub> are input and output vectors orderly. Quantum cost of MTSG gate is 6[9]. MTSG will be very useful to design reversible circuits as the quantum cost of the MTSG is very low as compared to the TSG gate[9], it is constricted from cascading of two Pares gates. By providing '0' in the D input, easily realize the full-adder from the MTSG gate. A reversible full adder can be realized at least one gate. For designing n-bit binary ripple carry adder n MTSG gates are required. The MTSG gate and its symbol is shown in figure 5.

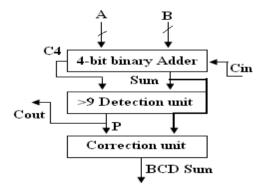

#### IV. Block Diagram of BCD Adder

A BCD adder is a circuit that adds two BCD numbers and produces a sum also in BCD form. Figure 6 shows the block diagram of BCD adder. A BCD adder must include three major parts. Those are

- (i) Binary adder (ii) Over 9 detection unit

- (iii) Correction unit

Binary adder performs addition operation on two BCD numbers and one-bit carry input. Over 9 detection unit recognizes if the result of first part is more 9or not. If the result is more than 9 it produces 1 otherwise 0. Correction unit, if the output of detector is 1then the sum is added by 6, else added by 0.

Figure 6: Block diagram of BCD adder

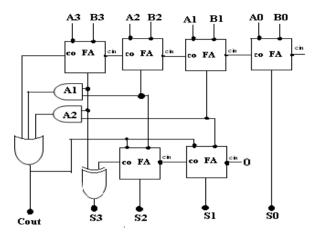

A conventional BCD adder is shown in figure 7. The first part 4-bit binary adder is cascade of four full adders. The second part detection unit is constructed by using two AND gates and one OR gate. The third part correction unit adds 0 to the binary number if the binary result is less than 10 and adds 6 to the binary result if it is more than 9. Binary full adder is a www.iimer.com

Vol.2, Issue.6, Nov-Dec. 2012 pp-4527-4531 ISSN: 2249-6645

basic circuit for designing binary arithmetic units such as n-bit binary adder, sub tractor and multiplier. In same manor a BCD adder/subtract or is a basic circuit for designing BCD arithmetic units such as BCD n-bit adder/sub tractor.

#### V. Efficient Design of Reversible BCD Adder

Figure 7: An irreversible BCD adder

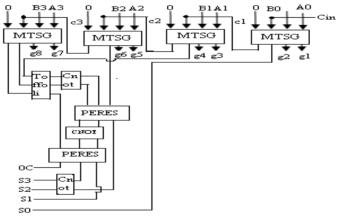

This is the equivalent design of the approach shown in figure 7. Proposed reversible BCD adder optimized for the number of reversible gates, memory usage and quantum cost. The proposed design of BCD adder is shown in figure 8. In first part 4 MTSG gates are connected in series. It can Work as 4-bit binary adder produce sum and carry [2]. Second part is equivalent design of over 9 detection unit and correction unit [8].

Figure 8: Proposed design of reversible BCD adder

#### 5.1. Quantum cost calculation

For n-bit proposed methodology needs n MTSG gates working in series thus in this stage has the quantum cost is 6n. In next stage (n-3) toffoli gates are working in series thus in this stage quantum cost is 5(n-3). In next stage (n-3) CNOT gates are working in series thus in this stage quantum cost is (n-3). In next stage (n-3) Peres gates are working in series thus in this stage quantum cost is 4(n-3). In next stage (n-3) CNOT gates are working in series thus in this stage quantum cost is (n-3). In next stage (n-3) Peres gates are working in series thus in this stage quantum cost is 4(n-3). In next stage (n-3) CNOT gates are working in series thus in this stage quantum cost is (n-3).

Thus the total quantum cost of n bit reversible BCD adder is 6n+5(n-3)+n-3+4(n-3)+n-3+4(n-3)+n-3=22n-48. In this paper we are discuss about 4-bit reversible BCD adder so quantum cost of proposed reversible BCD adder is 40. Number of reversible gates used in this design is 10.

#### VI. Results and Discussions

The proposed reversible BCD adder design has quantum cost 4 and delay is 11.228ns. To construct proposed BCD adder 10 reversible gates and 10 BELS and 6 slices are required. A comparison with the existing designs of the Reversible BCD adder is illustrated in Table 1. The design in [8] is the best existing design literature considering the Number of reversible gates, Quantum cost, Delay and BELS. It Needs 36 reversible gates and has the quantum cost 70 and it require 9 slices. The delay of design in [8] is 11.153ns, it can be observed from the comparison table that the proposed design is better than the design in [8] in terms of number of reversible gates, area, delay, quantum cost. Thus the proposed design is efficient compared to existing designs. Simulation Results of proposed Reversible BCD Adder is shown in figure 9. Apply a0 a1 a2 a3 is 0 0 1 1 respectively and similarly b0 b1 b2 b3 is 1 1 0 0 respectively and give the input carry is 0. It produces the result, carry out is 1 and s0 s1 s2 s3 is 0 1 0 1 respectively which is equivalent to the 15 in decimal form.

Vol.2, Issue.6, Nov-Dec. 2012 pp-4527-4531 ISSN: 2249-6645

TABLE 1 A Comparison of Reversible BCD Adders

| BCD      | No. of | No. Of | Quantm | Delay | BELS |

|----------|--------|--------|--------|-------|------|

| Adder    | slices | gates  | cost   | (ns)  |      |

| Existing | 9      | 36     | 70     | 12.15 | 22   |

| [14]     |        |        |        |       |      |

| Proposed | 6      | 10     | 40     | 11.22 | 10   |

| Design   |        |        |        |       |      |

#### VII. Conclusion

In this paper, reversible logic was implemented for BCD adder. By comparing the existing design with proposed design is less costly in terms of number of gates and quantum cost and delay and area and BELS. The proposed design is highly optimized. The efficient design of the BCD adder depends on the Design methodology used for designing the reversible ripple carry adder and the reversible binary to BCD converter. Thus for future research, efficient design schemes for reversible ripple carry adder and the reversible binary to BCD converter is an interesting area to investigate.

#### References

- [1] Himanshu Thapliyal, M.B.Srinivas, and M.Zwolinski, "A Beginning in the Reversible Logic Synthesis of Sequential Circuits", MAPLD

- [2] M. Thomsen and R.Gl"uck, "Optimized reversible binary-coded decimal adders," J. Syst. Archit., vol. 54, no. 7, pp. 697–706, 2008.

- [3] M. Mohammadi, M. Haghparast, M. Eshghi, and K. Navi, "Minimization optimization of reversible bcd-full adder/subtract or using genetic algorithm and don't care concept," International J. Quantum Information,

- [4] A. K. Biswas, M. M. Hasan, A. R. Chowdhury, and H. M. Hasan Babu, "Efficient approaches for designing reversible binary coded decimal adders," Microelectron. J., vol. 39, no. 12, pp. 1693–1703, 2008.

- [5] H.Thapliyal and N. Ranganathan, "Design of efficient reversible binarysubtractors based on a new reversible gate," in Proc. the IEEE Computer Society Annual Symposium on VLSI, Tampa, Florida, May 2009, pp.229–234.

- [6] Y. Takahashi and N. Kunihiro, "A linear-size quantum circuit for addition with no ancillary qubits," Quantum Information and Computation, vol. 5, no. 6, p. 440448, 2005.

- [7] Sreehari Veeramachaneni, M.Kirthi Krishna, Lingamneni Avinash, Sreekanth Reddy P, M.B.Srinivas "Novel, High-speed 16-Digit BCD Adders Conforming to IEEE 754r Format" IEEE Computer society Annual Symposium on VLSI 2007

- [8] Majid Mohammadi, Mohammad Eshghi, Majid Haghpaarast and Abbas "Design and of Reversible BCD Adder/Subtractor Circuit for Quantum and Nanotechnology Based systems" World applied Sciences Journal 4(6):787-792, 2008

- [9] M.A.Nielsen and I. L. Chuang, Quantum Computation and Quantum Information.NewYork: Cambridge Univ. Press, 2000.

- [10] T. Toffoli, "Reversible computing," MIT Lab for Computer Science, Tech. Rep. Tech memo MIT/LCS/TM-151, 1980.

- [11] A. Peres, "Reversible logic and quantum computers," Phys. Rev. A, Gen.Phys., vol. 32, no. 6, pp. 3266–3276, Dec. 1985.

- [12] H. Thapliyal and N. Ranganathan, "Design of reversible sequential circuits optimizing quantum cost, delay and garbage outputs," ACMJournal of Emerging Technologies in Computing Systems, vol. 6, no.4, Article 14, pp. 14:1–14:35, Dec. 2010.

- [13] S.A. Cuccaro, T. G. Draper, S. A. Kutin, and D. P. Moulton, "A new quantum ripple-carry addition circuit," http://arXiv.org/quantph/0410184, Oct 2004.

- [14] Y. Takahashi, S. Tani, and N. Kunihiro, "Quantum addition circuits" and unbounded fan-out," http://arxiv.org/abs/0910.2530, Oct 2009.

- [15] Himanshu Thapliyal, Nagarajan Ranganathan, "A New Reversible Design of BCD Adder" 978-3-9810801-7-9/DATE11/@2011 EDAA.